This article was downloaded by:

On: 25 January 2011

Access details: Access Details: Free Access

Publisher Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK

## Molecular Crystals and Liquid Crystals

Publication details, including instructions for authors and subscription information: http://www.informaworld.com/smpp/title~content=t713644168

# Fabrication of Atomic Layer Deposited Zinc Oxide Thin Film Transistors with Organic Gate Insulator on Flexible Substrate

Kyung Min Choi<sup>a</sup>; Gun Woo Hyung<sup>b</sup>; Jin Woo Yang<sup>c</sup>; Ja Ryong Koo<sup>c</sup>; Young Kwan Kim<sup>c</sup>; Sang Jik Kwon<sup>a</sup>; Eou Sik Cho<sup>a</sup>

<sup>a</sup> Department of Electronics Engineering, Kyungwon University, Seongnam-city, Kyunggi-do, Korea <sup>b</sup> Department of Material Science and Engineering, Hongik University, Mapo-gu, Seoul, Korea <sup>c</sup> Department of Information Display, Hongik University, Mapo-gu, Seoul, Korea

First published on: 14 November 2010

$\label{total continuous} \textbf{To cite this Article Choi, Kyung Min , Hyung, Gun Woo , Yang, Jin Woo , Koo, Ja Ryong , Kim, Young Kwan , Kwon, Sang Jik and Cho, Eou Sik(2010) 'Fabrication of Atomic Layer Deposited Zinc Oxide Thin Film Transistors with Organic Gate Insulator on Flexible Substrate', Molecular Crystals and Liquid Crystals, 529: 1, 131 <math display="inline">-$  136

To link to this Article: DOI: 10.1080/15421406.2010.495889 URL: http://dx.doi.org/10.1080/15421406.2010.495889

### PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: http://www.informaworld.com/terms-and-conditions-of-access.pdf

This article may be used for research, teaching and private study purposes. Any substantial or systematic reproduction, re-distribution, re-selling, loan or sub-licensing, systematic supply or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

Mol. Cryst. Liq. Cryst., Vol. 529: pp. 131–136, 2010 Copyright © Taylor & Francis Group, LLC

ISSN: 1542-1406 print/1563-5287 online DOI: 10.1080/15421406.2010.495889

# Fabrication of Atomic Layer Deposited Zinc Oxide Thin Film Transistors with Organic Gate Insulator on Flexible Substrate

KYUNG MIN CHOI,<sup>1</sup> GUN WOO HYUNG,<sup>2</sup> JIN WOO YANG,<sup>3</sup> JA RYONG KOO,<sup>3</sup> YOUNG KWAN KIM,<sup>3</sup> SANG JIK KWON,<sup>1</sup> AND EOU SIK CHO<sup>1</sup>

<sup>1</sup>Department of Electronics Engineering, Kyungwon University, Seongnam-city, Kyunggi-do, Korea

In the fabrication of transparent conductive oxide thin film transistor (TFT), an atomic layer deposited (ALD) zinc oxide (ZnO) and a cross-linked poly-vinylalcohol (c-PVA) were each used as active layer and gate insulating layer on poly-ethylene (PET) substrate respectively. Considering the transmittance and the deposition rate of the ALD ZnO at a low temperature without any damage on PET substrate, the ZnO layer was deposited at a temperature of  $120^{\circ}$ C on a spin-coated c-PVA layer. From the atomic force microscope (AFM) images, it was possible to conclude that the surface morphologies of ZnO deposited on a c-PVA layer was not inferior to those of ZnO deposited on bare-Si and that the c-PVA can be used as a gate insulator at  $120^{\circ}$ C. The fabricated ZnO TFT showed good electrical characteristics such as the mobility of  $0.1 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$ , on-off current ratio of  $4.5 \times 10^4$ .

**Keywords** Atomic layer deposition; c-poly vinyl alcohol; oxide tft; PET substrate; zinc oxide

#### Introduction

Recently, a lot of achievements have been obtained in the researches and developments of zinc oxide (ZnO) for the application to the devices such as various sensors, solar cells, electronic and optical devices, and flat panel displays [1–6]. Especially, zinc oxide has been used as an active layer of thin film transistor (TFT) because it

Address correspondence to Eou Sik Cho, Assistant Professor, Department of Electronics Engineeing, Kyungwon University, San 65, Bokjung-dong, Soojung-gu, Seongnam-city, Kyunggi-do 461-701, Korea (ROK). Tel.: (+82)31-750-5297; Fax: (+82)31-750-8696; E-mail: es.cho@kyungwon.ac.kr

<sup>&</sup>lt;sup>2</sup>Department of Material Science and Engineering, Hongik University, Mapo-gu, Seoul, Korea

<sup>&</sup>lt;sup>3</sup>Department of Information Display, Hongik University, Mapo-gu, Seoul, Korea

has an excellent transparency in a range of wavelengths of visible rays due to its wide band gap, higher mobility and on/off ratio than conventional hydrogenated amorphous silicon (a-Si:H) TFT in spite of the lower process temperature [7–11].

For the application of ZnO TFT to flexible displays, it is indispensable to use flexible substrates such as polycarbonate (PC) and poly-ethylene (PET) instead of a glass substrate. The flexible substrates are easily degraded by heat and chemicals during deposition and wet chemical etching used in conventional fabrication process. For the compatibility to the flexible substrate, it is necessary to use low temperature process such as spin-coating used in the fabrication of organic TFT (OTFT). Poly-vinyl-alcohol (PVA) has been used as gate insulating layer of OTFT by spin coating process because of its high dielectric constant, resistance to solvent during lift-off process, and the effect of good surface alignment [12–14].

In this research, spin coated PVA was applied to gate insulating layer in the fabrication of ZnO TFT on PET substrate. ZnO layer was deposited on PVA gate insulator at a low temperature by using atomic layer deposition (ALD) instead of sputtering to avoid the damage on PVA layer during sputtering process. The fabricated ALD ZnO TFT with PVA gate insulator on PET substrate was electrically characterized.

#### **Experimental**

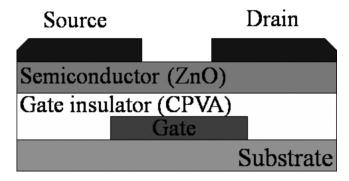

A bottom gated ZnO TFT was fabricated on PET substrate as shown in Figure 1 [15–16]. As a gate electrode, Al was thermally evaporated with a thickness of 100 nm through a shadow mask. Then 3% PVA solution mixed with an ammonium dichromate was spin coated and an ultraviolet (UV) lamp was used to obtain cross-linked PVA for better immunity to moisture. During ALD process of ZnO active layer, diethylzinc (DEZn, Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>) and deionized water (H<sub>2</sub>O) were used as a zinc precursor and an oxygen precursor, respectively. The DEZn and H<sub>2</sub>O were maintained at room temperature and the PET substrate was maintained at temperature enough to avoid any deformation or damages on PET substrate. The injection times of DEZn and H<sub>2</sub>O were kept at 1 sec respectively and the Ar purging time was kept at 6 sec for each injection. As a formation of source and drain on 50 nm ZnO active layer, Al was deposited with a thickness of 60 nm to a through a shadow mask. The width and the length of fabricated TFT were designed as 300 μm and 100 μm,

Figure 1. A schematic diagram of the fabricated ZnO-TFT with cross-linked PVA gate insulator on PET substrate.

respectively. For the electrical characterization of the fabricated ZnO TFT, a probe station and Agilent 4156C were used in the measurement.

#### **Results and Discussion**

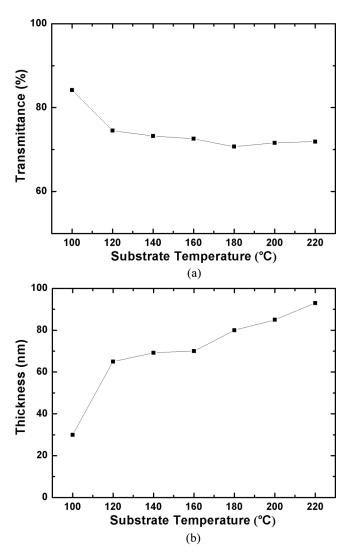

To optimize the deposition temperature of ALD ZnO layer, ZnO was deposited at various substrate temperatures from 100°C to 220°C. Figure 2(a) shows the average transmittances of the ZnO layers deposited at various temperatures from 400 nm to 800 nm of light. The ZnO layers were deposited on soda-lime glass substrates for 100 cycles and 1 cycle was composed of the injections of DEZn and H<sub>2</sub>O sources and the purge process of Ar gas. From the results, the average transmittance

**Figure 2.** (a) Optical transmittance of ZnO thin film grown on by ALD at different temperature (b) Thickness of ZnO thin film of (a).

abruptly decreases between 100°C and 120°C and slightly decreases as the substrate temperature increases above 120°C. Considering that more ZnO molecules crystallize at higher temperature, it is possible to conclude that the transmittance is related to the thickness of the ZnO layer. Figure 2(b) shows the thickness of the ZnO layer of Figure 2(a). As all the ZnO was deposited for 100 cycles (1400 sec), it is possible to consider the result as the deposition rate of ALD ZnO. The deposition rate abruptly increases from about 3 Å/cycle to 6.5 Å /cycle between 100°C and 120°C and slightly increases as the substrate temperature increases above 120°C. Considering the transmittance and the deposition rate, and the temperature (<150°C) enough to avoid any deformation of PET substrate, ZnO was deposited on c-PVA at 120°C. However, the ALD process was carried out for about 75 cycles to optimize the thickness of active layer as 50 nm.

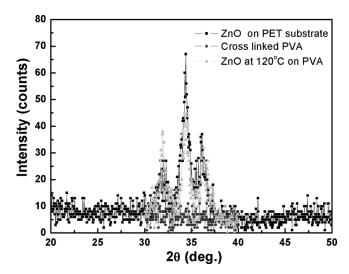

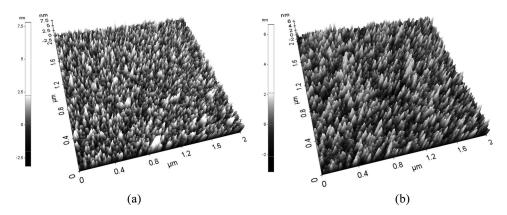

Figure 3 shows the X-ray diffraction (XRD) spectrum of ZnO layer, c-PVA, and ZnO on c-PVA on PET substrate. From the results, a main peak at 34.4° and two sub peaks at 32° and 36.2° were obtained for both the ZnO and the ZnO on c-PVA layer. A main peak at 34.4° indicates the ZnO(200) peak and two sub peaks the ZnO(100) and ZnO(101) peak at at 32° and 36.2°, respectively [17]. There were no degradations on the structure of ZnO layer on c-PVA layer. Figure 4 shows the surface morphologies of the ZnO layer deposited on bare substrate and the ZnO layer on c-PVA layer. The surface roughnesses of two ZnO layers were obtained as 0.848 nm and 0.859 nm for Figures 4(a) and 4(b), respectively. It is possible to describe that ZnO layers are initially formed on the surface of c-PVA without any deformation of c-PVA molecules because of low deposition temperature of 120°C.

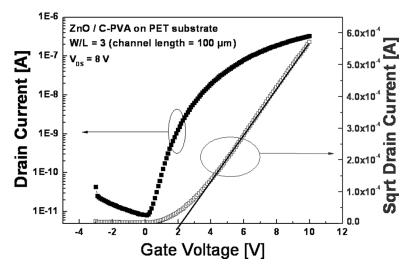

Figure 5 shows the transfer characteristics of the fabricated TFT. When drain voltage was 8 V, the ZnO TFT showed a mobility of about  $0.1 \,\mathrm{cm^2/V \cdot sec}$ , on/off current ratio of  $4.5 \times 10^4$ , and a threshold voltage of 2 V. Considering the process temperature less than  $120^{\circ}$ C, the electrical characteristics are adequate for the application to active matrix device. However, it is required to investigate the effect of

**Figure 3.** XRD spectrums of ZnO thin film on PET substrate, cross-linked PVA on PET substrate, and ZnO thin film on cross-linked PVA on PET substrate. ZnO was deposited at the substrate temperature of 120°C.

Figure 4. AFM images of ZnO layer on (a) base Si and (b) cross-linked PVA.

c-PVA on PET substrate and low temperature deposited ZnO on the electrical characteristics such as hysteresis and threshold voltage shift.

#### Conclusion

For the fabrication of ZnO TFT on flexible PET substrate, c-PVA gate insulator was spin coated on the PET substrate and ZnO active layer was deposited on c-PVA layer at low temperature enough to avoid any deformation of c-PVA layer and PET substrate. To optimize the process condition of ZnO deposition, process temperature was determined through the investigation of transmittance and deposition rate. Through XRD results and AFM images of ZnO layer on c-PVA insulator, it was possible to conclude the ALD process does not have an effect on the c-PVA layer or on PET substrate. The fabricated ZnO TFT showed good electrical

Figure 5. Electrical characteristics of fabricated ZnO-TFT with PVA gate insulator.

characteristics in spite of low temperature process. Further investigation and analysis are needed to confirm the stability of ZnO TFT.

#### Acknowledgments

This work was supported by the Korean Research Foundation (KRF) grant funded by the Korean government (MEST) (No. 2009-0076193). This work was also supported by the Kyungwon University Research Fund in 2009. This work was supported by the BK21 program and the ERC program of the Korea Science and Engineering Foundation (KOSEF) grant funded by the Korean Ministry of Education, Science and Technology (MEST) (No. R11-2007-045-03001-0).

#### References

- [1] Arya, S. P. S., & Srivastava, O. N. (1988). Cryst. Res. Technol., 23, 669.

- [2] Lee, C., Lim, K., & Song, J. (1996). Sol. Energy. Mater. Sol. Cells., 43, 37.

- [3] Bae, H. S., & Im, S. (2004). Thin Solid Film, 469, 75.

- [4] Harza, S. K., & Basu, S. (2005). Solid State Electron., 49, 1158.

- [5] Assuncao, V., Fortunato, E., Marquis, H., Angus, A., Ferreira, I., Costa, M. E. V., & Martins, R. (2003). Thin Solid Film, 427, 401.

- [6] Jager, S., Szyszka, B., Szczyrbowski, J., & Bauer, G. (1998). Surf. Coat. Technol., 98, 1304.

- [7] Navamathan, R., Lim, J., Hwang, D., Kim, B., Oh, J., Yang, J., Kim, H., & Park, S. (2006). J. Korean. Phys. Soc., 48, 271.

- [8] Fortunato, E., Barquinha, P., Pimental, A., Concalves, A., Marques, A., Martins, R., & Pereira, L. (2004). *Appl. Phys. Lett.*, 85, 2541.

- [9] Masuda, S, Kitamura, K., Okumura, Y., & Miyatake, S. (2003). J. Appl. Phys., 93, 1624.

- [10] Hoffman, R. L., Norris, B. J., & Wager, J. F. (2003). Appl. Phys. Lett., 82, 733.

- [11] Carcia, P. F., McLean, R. S., Reily, M. H., & Nunes, G. (2003). Appl. Phys. Lett., 82, 1117.

- [12] Peng, X., Horowitz, G., Fichou, D., & Carnier, F. (1990). Appl. Phys. Lett., 57, 2013.

- [13] Swiggers, M. L., Xia, G., Slinker, J. D., Gorodetsky, A. A., & Malliaras, G. G. (2001). Appl. Phys. Lett., 79, 1300.

- [14] Jin, S. H., Yu, J. S., Lee, C. A., Kim, J. W., Park, B.-G., & Lee, J. D. (2004). J. Korean. Phys. Soc., 44, 181.

- [15] Choi, K. M., Hyung, G. W., Cho, E. S., Koo, J. R., Kim, Y. K., & Kwon, S. J. (2009). The 13th ADMD Program and Abstract, 187.

- [16] Choi, K. M., Hyung, G. W., Ahn, M. H., Li, Z.-H., Jung, K. S., Kim, Y. K., Kwon, S. J., & Cho, E. S. (2009). *The Extended Abstract of IWFPE 2009*, 155.

- [17] Hernandez, C. V., Garcia, F. N. J., Jurado, J. F., & Dranada, V. H. (2008). Microelectronics Journal, 39, 1347.